# **3-Phase Sinusoidal Motor Controller**

# **Features and Benefits**

- Sinusoidal Drive Current

- Hall Element Inputs

- PWM Current Limiting

- Dead-time Protection

- FGO (Tach) Output

- Internal UVLO

- Thermal Shutdown Circuitry

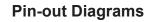

# Packages: 32-Pin QFN (suffix ET)

Not to scale

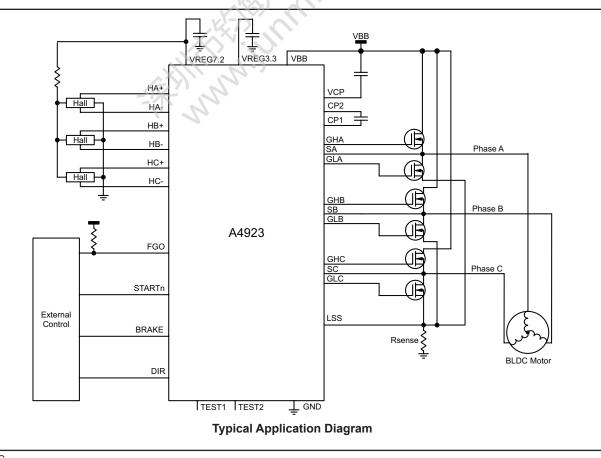

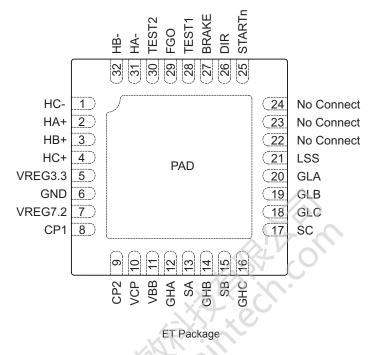

Designed to control three-phase brushless DC motors, the A4923 is capable of high-current gate drive for an all N-channel power MOSFET 3-phase bridge.

Sinusoidal current control is employed via output PWM, to minimize vibration, noise, and torque ripple.

Internal circuit protection includes thermal shutdown with hysteresis, over-current, and dead-time protection. Special power up sequencing is not required.

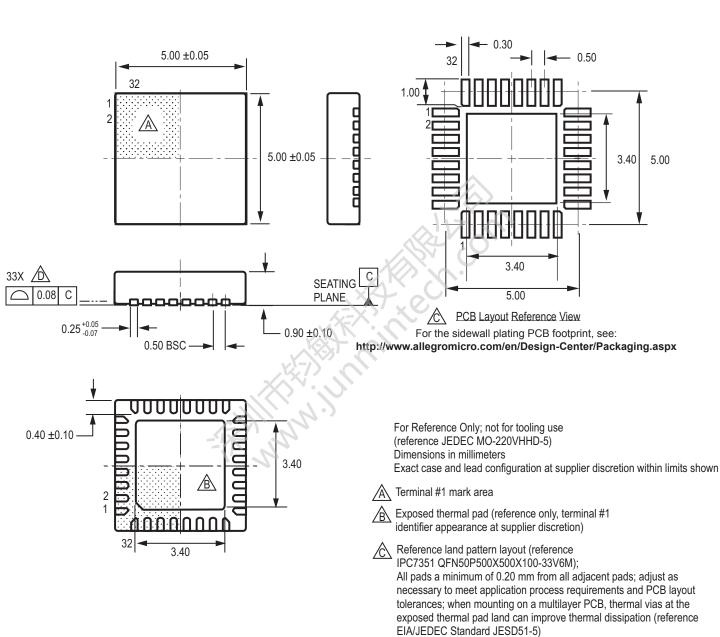

The A4923 is supplied in a 32 terminal  $5 \times 5 \times 0.9$ mm QFN package (suffix ET) with exposed pad for enhanced thermal dissipation. This small footprint package is lead (Pb) free with 100% matte tin leadframe plating, and it is also available with optional sidewall plating.

# **3-Phase Sinusoidal Motor Controller**

#### **Selection Guide**

| Part Number                  | Package                                 | Packing              | Sidewall Plating |

|------------------------------|-----------------------------------------|----------------------|------------------|

| A4923GETTR-T                 | 5 mm X 5 mm, 0.90 mm nominal height QFN | 1500 pieces per reel | No               |

| A4923GETTR-R*                | 5 mm X 5 mm, 0.90 mm nominal height QFN | 1500 pieces per reel | Yes              |

| *Contact factory for availab | hilith (                                | 1                    | 1                |

Contact factory for availability

#### **Absolute Maximum Ratings**

| Characteristic                         | Symbol           | Notes   | Rating     | Unit |

|----------------------------------------|------------------|---------|------------|------|

| Supply Voltage                         | V <sub>BB</sub>  |         | 36         | V    |

| Logic Input Voltage Range              | V <sub>IN</sub>  |         | –0.3 to 6  | V    |

| Logic Outputs                          | Vo               |         | 6          | V    |

| Junction Temperature                   | Тј               |         | 150        | °C   |

| Operating Ambient Temperature<br>Range | T <sub>A</sub>   | Range G | -40 to 105 | °C   |

| Storage Temperature Range              | T <sub>stg</sub> | XXXX    | –55 to 150 | °C   |

#### Thermal Characteristics may require derating at maximum conditions, see application information

| Characteristic                      | Symbol          | Test Conditions*                         | Value | Unit |

|-------------------------------------|-----------------|------------------------------------------|-------|------|

| Package Thermal Resistance A4923GET | $R_{\theta JA}$ | On 2-sided PCB, 1 in <sup>2</sup> copper | 50    | °C/W |

|                                     |                 | On 4-layer PCB                           | 32    | °C/W |

\*Additional thermal information available on the Allegro website.

# A4923

# **3-Phase Sinusoidal Motor Controller**

#### **Terminal List Table**

| Name    | Function                           | Number | Name   | Function                                           | Number |

|---------|------------------------------------|--------|--------|----------------------------------------------------|--------|

| HC-     | Analog hall input C                | 1      | SC     | High-side source connection C                      | 17     |

| HA+     | Analog hall input A                | 2      | GLC    | Low-side gate drive C                              | 18     |

| HB+     | Analog hall input B                | 3      | GLB    | Low-side gate drive B                              | 19     |

| HC+     | Analog hall input C                | 4      | GLA    | Low-side gate drive A                              | 20     |

| VREG3.3 | 3.3V regulator capacitor terminal  | 5      | LSS    | Low-side sense resistor connection                 | 21     |

| GND     | Ground                             | 6      | -      | No connect                                         | 22     |

| VREG7.2 | 7.2V regulator capacitor terminal  | 7      | -      | No connect                                         | 23     |

| CP1     | Charge pump capacitor terminal     | 8      | -      | No connect                                         | 24     |

| CP2     | Charge pump capacitor terminal     | 9      | STARTn | Digital start input                                | 25     |

| VCP     | Charge pump reservoir cap terminal | 10     | DIR    | Digital direction input                            | 26     |

| VBB     | Supply voltage                     | 11     | BRAKE  | Digital brake input                                | 27     |

| GHA     | High-side gate drive A             | 12     | TEST1  | ATE terminal, can be left open or connected to GND | 28     |

| SA      | High-side source connection A      | 13     | FGO    | Digital motor-speed output                         | 29     |

| GHB     | GHB High-side gate drive B         |        | TEST2  | ATE terminal, can be left open or connected to GND | 30     |

| SB      | High-side source connection B      | 15     | HA-    | Analog hall input A                                | 31     |

| GHC     | High-side gate drive C             | 16     | HB-    | Analog hall input B                                | 32     |

|         |                                    |        | PAD    |                                                    | -      |

# **3-Phase Sinusoidal Motor Controller**

# **ELECTRICAL CHARACTERISTICS** Valid at $T_A = 25^{\circ}C$ , unless otherwise specified

| Characteristic                | Symbol                 | Test Conditions                    | Min. | Тур. | Max. | Unit  |

|-------------------------------|------------------------|------------------------------------|------|------|------|-------|

| Supply and Reference          |                        |                                    |      |      |      |       |

| VBB Voltage Range             | V <sub>BB</sub>        |                                    | 10   | -    | 32   | V     |

| VBB Supply Current            | I <sub>BB</sub>        |                                    | -    | 18   | 22   | mA    |

| VREG3.3 Voltage               | V <sub>REG3.3</sub>    | I = 0 to -5 mA                     | 2.9  | 3.3  | 3.5  | V     |

| VREG7.2 Voltage               | V <sub>REG7.2</sub>    | Gate Drive Supply, I = 0 to -24 mA | 6.8  | 7.2  | 7.6  | V     |

| VREG7.2 Current Limit         | I <sub>LIMREG7.2</sub> |                                    | -30  | -    | _    | mA    |

| Logic Inputs                  | ·                      | STARTn, DIR, BRAKE                 |      |      |      |       |

| Logic Input Low Level         | V <sub>IL</sub>        |                                    | 0    | _    | 0.8  | V     |

| Logic Input High Level        | V <sub>IH</sub>        |                                    | 2.0  | -    | 5.5  | V     |

| Logic Input Hysteresis        | V <sub>HYS</sub>       |                                    | -    | 350  | _    | kHz   |

|                               | R <sub>IN</sub>        | Pull-up to internal 3.3V           | 34   | 47   | 60   | kΩ    |

| Logic Input Current           | I <sub>IN(1)</sub>     | V <sub>IN</sub> = 5 V              | - 1  | 36   | _    | μA    |

|                               | I <sub>IN(0)</sub>     | V <sub>IN</sub> = 0 V              | -    | -70  | _    | μA    |

| Logic Outputs                 |                        | FGO                                |      |      |      |       |

| Output Saturation Voltage     | V <sub>SAT</sub>       | I = -7 mA                          | -    | 0.14 | 0.21 | V     |

| Output Leakage                | I <sub>FGO</sub>       | V = 3.3 V                          | -    | -    | 1    | μA    |

| Halls                         |                        |                                    |      |      |      |       |

| Hall Input Current            | I <sub>HALL</sub>      | V <sub>IN</sub> = 0.2 V to 3.4 V   | -1   | 0    | 1    | μA    |

| Common Mode Input Range       | V <sub>CMR</sub>       |                                    | 0.2  | -    | 3.4  | V     |

| AC Input Voltage Range        | V <sub>HALL</sub>      |                                    | 50   | -    | _    | mVp-p |

| Hall Digital Filter Time      | t <sub>HALL</sub>      | $\infty$                           | _    | 1.6  | _    | μs    |

| Gate Drive                    |                        | 1.7.                               |      |      |      |       |

| PWM Carrier Frequency         | f <sub>PWM</sub>       | 2                                  | 19   | 20   | 21   | kHz   |

| Current Limit Input Threshold | V <sub>LSS</sub>       | Threshold on LSS terminal          | 216  | 240  | 256  | mV    |

| Gate Drive Output Voltage     | V <sub>GS</sub>        | I <sub>GATE</sub> = -2 mA          | 6.0  | 6.9  | _    | V     |

| Gate Drive Source Current     | IG <sub>SRC</sub>      | V <sub>GX</sub> = 4 V              | -21  | -30  | -39  | mA    |

| Gate Drive Sink Current       | IG <sub>SNK</sub>      | V <sub>GX</sub> = 4 V              | 50   | 70   | 90   | mA    |

| Gate Pulldown, Passive        | R <sub>PULLDOWN</sub>  |                                    | -    | 300  | _    | kΩ    |

| Dead Time                     | t <sub>DEAD</sub>      |                                    | 1460 | -    | 1880 | μs    |

| Fixed Off-time                | t <sub>OFF</sub>       |                                    | 21.0 | -    | 27.5 | μs    |

| LSS Digital Filter Time       | t <sub>BLANK</sub>     |                                    | 720  | -    | 880  | μs    |

| Protection                    | · ·                    |                                    |      |      |      |       |

| Thermal Shutdown Temperature  | T <sub>JTSD</sub>      |                                    | -    | 130  | _    | °C    |

| Thermal Shutdown Hysteresis   | $\Delta T_{JTSD}$      |                                    | -    | 10   | _    | °C    |

| VBB UVLO Threshold            | V <sub>UVLO</sub>      | Rising V <sub>BB</sub>             | -    | 7.0  | 7.85 | V     |

| VBB UVLO Hysteresis           | V <sub>UVLOHYST</sub>  |                                    | 0.5  | 0.75 | 1.0  | V     |

NOTES:

1. Typical Data is for design information only.

2. Negative current is defined as coming out of (sourcing) the specified device terminal.

3. Specifications over operating temperature range are assured by design and characterization.

A4923

# **Functional Description**

## STARTn

The STARTn terminal is the active-low start/stop logic input. (low = start, high = all gate drive outputs off). Internally pulled up to VREG3.3.

### BRAKE

The BRAKE terminal is the active-high logic input to turn on all low-side MOSFETs. The STARTn terminal must be active (low) to enable brake. Internally pulled up to VREG3.3

### DIR

The DIR terminal is the logic input to control the motor's direction. A logic high = FWD and a logic low = REV. Internally pulled up to VREG3.3.

#### Table 1:

| STARTn | BRAKEn | Fault | Function             |

|--------|--------|-------|----------------------|

| Н      | Х      | L     | All gate outputs low |

| L      | L      | L     | Run                  |

| L      | Н      | L     | Brake                |

| X      | Х      | Н     | All gate outputs low |

#### FGO

The FGO terminal is an open-drain logic output which toggles state each hall transition.

## TEST1, TEST2

The TEST1 and TEST2 terminals are for ATE testing and can be left open or tied to GND.

#### **Current Limit**

Over-current is controlled by an internal fixed off-time PWM control circuit. At the trip point, the sense comparator turns off

the enabled low-side driver, turns on the corresponding high side driver, and the motor current recirculates through the high-side drivers.

$$ITRIP = 240 \ mV / R_{SENSE}$$

#### Hall Inputs

Unique circuitry incorporates hysteresis which toggles polarity with the hall input slope direction. This allows the hall comparators to operate with very small offsets and results in highly symmetrical comparator outputs. A digital filter on the hall inputs minimizes sensitivity to noise.

### VPOS

A 0.1  $\mu$ F capacitor is required between this terminal and GND to stabilize the internal 3.3 V regulator

## VREG

A 0.1  $\mu$ F capacitor is required between this terminal and GND to stabilize the low-side gate supply.

## **Charge Pump**

Terminals CP1, CP2, and VCP generate a voltage above VBB that is used for the high-side gate supply. A 0.1  $\mu$ F capacitor is required between the CP1 and CP2 terminals, and between VCP and VBB.

#### Fault

A fault occurs when VBB, the charge pump, or HBIAS falls below the respective UVLO threshold, the device temperature rises above  $T_J$ , or the hall inputs indicate an invalid state (111 or 000). The outputs are disabled in the event of a fault. Faults are not latched, and the device resumes operation once the fault is cleared.

## Sine Mode

When the motor is stopped, a Hall Timeout error exists since the hall-transition timer has timed out. When a start signal is applied via the STARTn terminal, the motor is enabled in trapezoidal mode. When two consecutive hall transitions do not overflow the hall-transition timer, the Hall Timeout error is cleared and the drive switches to sinusoidal mode.

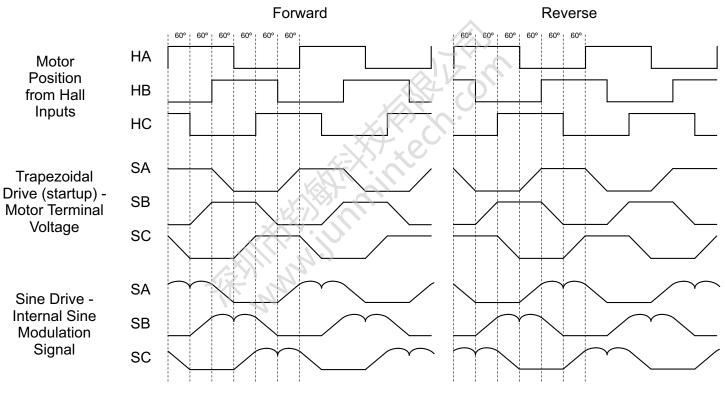

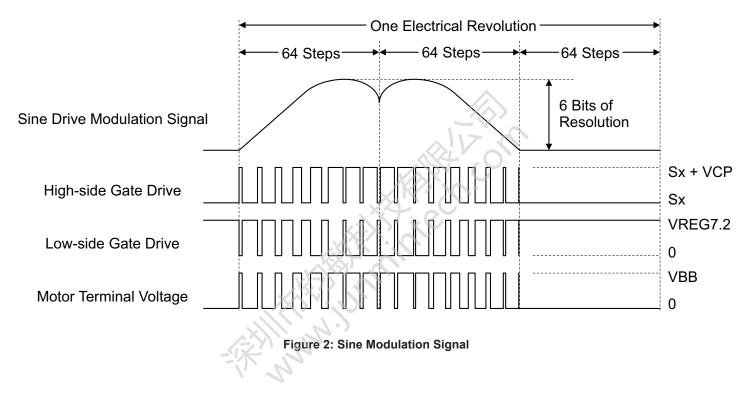

The sine modulation profile is stored in a digital look-up table. The sine modulation value is updated from the profile 192 times per electrical revolution. At each hall transition, which occurs every  $60^{\circ}$  or every 32 steps, the profile index is forced to the appropriate step. It is then advanced the successive 32 steps with a timer set internally using the previous hall transition period. The motor outputs are generated as follows (phase advance is not shown to simplify this diagram):

Figure 1: Motor Outputs

The internal sine modulation signal is converted to a PWM signal to drive the motor terminals. A 20 kHz carrier is modulated with the current sine profile value and used to generate the gate drive signals. Thus, the motor terminal voltage is a 20 kHz PWM signal with a duty cycle dependent upon the sine modulation signal. The high- and low-side gate drivers on a given motor terminal are

enabled inverted of the other, with a dead-time added to ensure both drivers will never be enabled at the same time. For increased efficiency, torque ripple, and audible noise, the sine profile is advanced 7.5° of one electrical revolution, relative to the hall transitions.

Package ET, 32-Pin QFN with Exposed Thermal Pad

WWW. Junning

Copyright ©2012-2014, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.